**SoC Blockset™**

Reference

# MATLAB® SIMULINK®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

T

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

SoC Blockset™ Reference

© COPYRIGHT 2019 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### **Patents**

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

March 2019 Online Only New for Version 1.0 (Release 2019a)

## Contents

Blocks

1

## **Configuration Parameters**

2

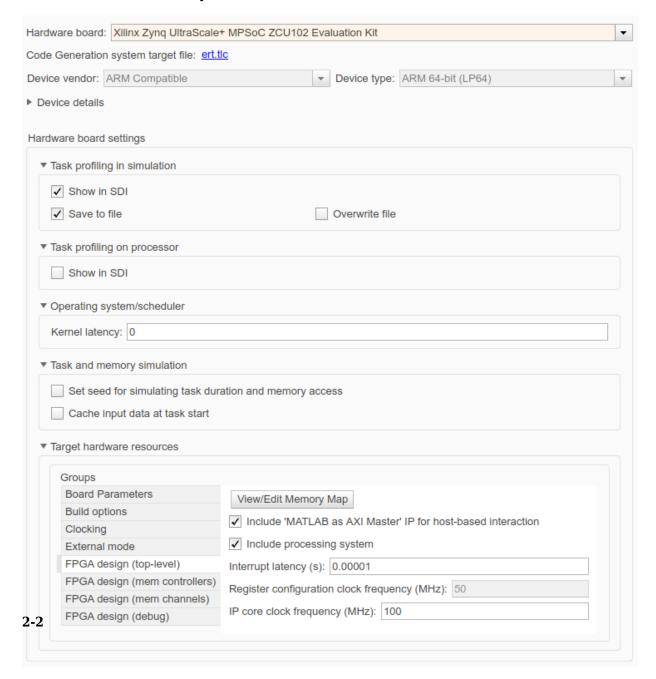

|                                         | 2-2         |

|-----------------------------------------|-------------|

| Hardware Implementation Pane Overview   | <b>2-</b> 2 |

| Task Profiling in Simulation            | <b>2-</b> 3 |

| Task Profiling on Processor             | <b>2-</b> 3 |

|                                         | 2-3         |

|                                         | <b>2-</b> 3 |

|                                         | - 3<br>2-4  |

|                                         | <br>2-4     |

|                                         | 2-5<br>2-5  |

|                                         | 2-6<br>2-6  |

| FDCA design (debug)                     | 2-0<br>2-6  |

|                                         |             |

| Feature set for selected hardware board | <b>2-</b> 7 |

| T I D CH I CH I H                       |             |

|                                         | 2-8         |

|                                         | 2-8         |

| Save to file                            | 2-8         |

| Overwrite file                          | 2-8         |

|                                         |             |

| Task Profiling on Hardware              | <b>2-</b> 9 |

| Show in SDI                             | 2-9         |

| Save to file                            | 2-9         |

|                                         | <b>2-</b> 9 |

| Kernel Latency                          | -10         |

|                                         | -10         |

| =g                                      |             |

| Task and Memory Simulation                              | 2-11 |

|---------------------------------------------------------|------|

| Set seed for simulating task duration and memory access | 2-11 |

| Seed Value                                              | 2-11 |

| Cache input data at task start                          | 2-11 |

| Processor                                               | 2-12 |

| Number of cores                                         | 2-12 |

| FPGA design (top-level)                                 | 2-13 |

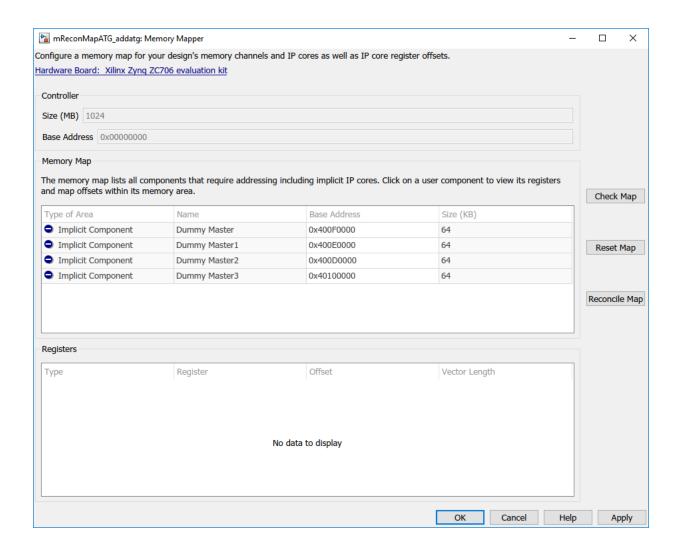

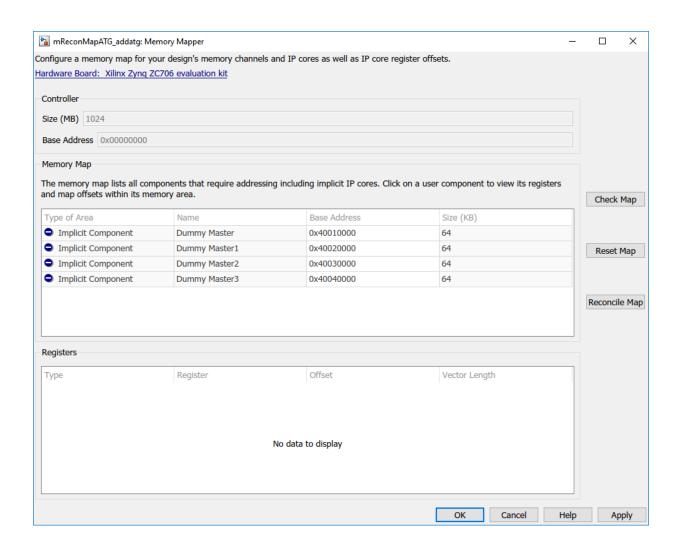

| View/Edit Memory Map                                    | 2-13 |

| Include a JTAG master for host-based interaction        | 2-13 |

| Include processing system                               | 2-13 |

| Interrupt latency (s)                                   | 2-13 |

| Register configuration clock frequency (MHz)            | 2-14 |

| IP core clock frequency (MHz)                           | 2-14 |

| FPGA design (mem controllers)                           | 2-15 |

| Controller clock frequency (MHz)                        | 2-15 |

| Controller data width (bits)                            | 2-15 |

| Bandwidth derating (%)                                  | 2-15 |

| First write transfer latency (clocks)                   | 2-15 |

| Last write transfer latency (clocks)                    | 2-16 |

| First read transfer latency (clocks)                    | 2-16 |

| Last read transfer latency (clocks)                     | 2-17 |

| FPGA design (mem channels)                              | 2-18 |

| Interconnect clock frequency (MHz)                      | 2-18 |

| Interconnect data width (bits)                          | 2-18 |

| Interconnect FIFO depth (num bursts)                    | 2-18 |

| Interconnect almost-full depth                          | 2-18 |

| FPGA design (debug)                                     | 2-19 |

| Memory channel diagnostic level                         | 2-19 |

| Include AXI interconnect monitor                        | 2-19 |

| Trace capture depth                                     | 2-19 |

| Functions                 | <b>3</b>   |

|---------------------------|------------|

| Objects                   | <b>4</b> [ |

| Tools — Alphabetical List | <b>5</b> [ |

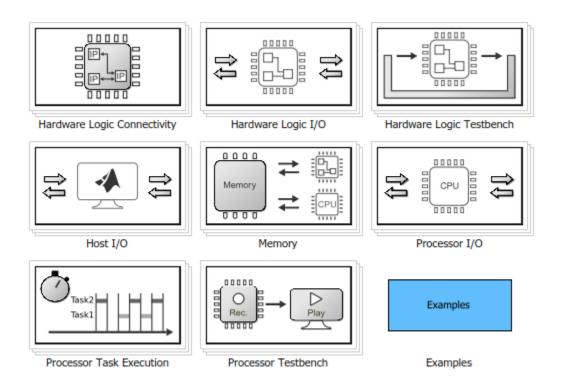

## **Blocks**

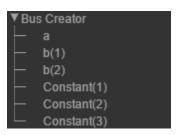

## **SoC Bus Creator**

Convert control signals to bus

**Library:** SoC Blockset / Hardware Logic Connectivity

## **Description**

The SoC Bus Creator block combines a set of signals into a bus. The block accepts control signals and outputs a bus.

You can configure this block to support multiple protocol interface types. Parameter and port configurations for this block vary based on your desired protocol interface type and mode of operation, as outlined in this table.

| Protocol<br>Interface<br>Type       | Mode of<br>Operation | Parameter Configuration                                                             | Enabled Input Ports |

|-------------------------------------|----------------------|-------------------------------------------------------------------------------------|---------------------|

| Data stream                         | Read data stream     | Set <b>Control protocol</b> to <b>Data</b> stream and <b>Control type</b> to Ready. | ready               |

|                                     | Write data           | Set <b>Control protocol</b> to Data                                                 | valid               |

|                                     | stream               | stream and <b>Control type</b> to Valid.                                            | tlast               |

| Pixel stream                        | Read video<br>stream | Set Control protocol to Pixel stream and Control type to Ready.                     | ready               |

| Write video Set Control protocol to |                      | hStart                                                                              |                     |

|                                     | stream               | Pixel stream and Control type to Valid.                                             | hEnd                |

|                                     |                      |                                                                                     | vStart              |

|                                     |                      |                                                                                     | vEnd                |

|                                     |                      |                                                                                     | valid               |

| Protocol<br>Interface<br>Type | Mode of<br>Operation                           | Parameter Configuration                                        | Enabled Input Ports                                  |        |

|-------------------------------|------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|--------|

|                               | Read video                                     | Set Control protocol to                                        | ready                                                |        |

|                               | stream with<br>frame sync                      | Pixel stream and <b>Control type</b> to Ready frame with sync. | fsync                                                |        |

| Random                        |                                                |                                                                | rd_addr                                              |        |

| access read                   |                                                |                                                                | Random access read and <b>Control type</b> to Ready. | rd_len |

|                               |                                                | Control type to Ready.                                         | rd_avalid                                            |        |

|                               |                                                |                                                                | rd_dready                                            |        |

| Random                        | Write data                                     | Set Control protocol to                                        | wr_addr                                              |        |

| access write                  | Random access write and Control type to Valid. | wr_len                                                         |                                                      |        |

|                               |                                                | Control type to vactu.                                         | wr_valid                                             |        |

## **Ports**

## Input

#### valid — Valid control signal

Boolean scalar

Valid control signal, specified as a scalar. You can use this port for data stream and pixel stream protocols only.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### tlast — Indication of end of data packet

Boolean scalar

Indication of end of the data packet, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Data stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### ready — Ready control signal

Boolean scalar

Ready control signal, specified as a Boolean scalar. This port is available for Data stream and Pixel stream control protocols.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Ready or Ready with frame sync.

Data Types: Boolean

#### hStart — First pixel in horizontal line of frame

Boolean scalar

First pixel in a horizontal line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### hEnd — Last pixel in horizontal line of frame

Boolean scalar

Last pixel in a horizontal line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### vStart — First pixel in first (top) line of frame

Boolean scalar

First pixel in the first (top) line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### vEnd — Last pixel in last (bottom) line of frame

Boolean scalar

Last pixel in the last (bottom) line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### fsync — Frame synchronization

Boolean scalar

Frame synchronization, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Ready with frame sync.

Data Types: Boolean

#### rd\_addr — Reader address

scalar

Reader address, specified as a scalar. It is the starting address for the read transaction that is sampled at the first cycle of the transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: uint32

#### rd len - Reader data length

scalar

Reader data length, specified as a scalar. It means the number of data values that you want to read, sampled at the first cycle of the transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: uint32

#### rd\_avalid — Reader valid status

Boolean scalar

Reader valid status, specified as a Boolean scalar. It indicates whether the read request is valid.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### rd\_dready — Reader ready status

Boolean scalar

Reader ready status, specified as a Boolean scalar. It indicates when the hardware logic can start accepting data.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### wr\_addr — Writer address

scalar

Specify the starting address to which the hardware writes.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: uint32

#### wr\_len — Writer data length

scalar

Specify the number of data elements in the write transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: uint32

#### wr valid — Writer valid data

Boolean scalar

Writer valid data, specified as a scalar. It indicates the data signal sampled at the output is valid.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

## **Output**

#### ctrlBus — Output control bus

bus

Output control bus, returned as a bus.

The data type of the output control bus depends on the values of the **Control protocol** and **Control type** parameters.

| Parameter Configuration                                                      | Output Data Type |

|------------------------------------------------------------------------------|------------------|

| Set <b>Control protocol</b> to Data stream and <b>Control type</b> to Ready. | StreamS2MBus0bj  |

| Set <b>Control protocol</b> to Data stream and <b>Control type</b> to Valid. | StreamM2SBusObj  |

| Parameter Configuration                                                                       | Output Data Type          |

|-----------------------------------------------------------------------------------------------|---------------------------|

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Ready.                 | StreamVideoS2MBusObj      |

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Valid.                 | pixelcontrol              |

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Ready frame with sync. | StreamvideoFsyncS2MBus0bj |

| Set <b>Control protocol</b> to Random access read and <b>Control type</b> to Ready.           | ReadControlM2SBusObj      |

| Set <b>Control protocol</b> to Random access write and <b>Control type</b> to Valid.          | WriteControlM2SBusObj     |

Data Types: StreamS2MBus0bj | StreamM2SBus0bj | StreamVideoS2MBus0bj | pixelcontrol | StreamvideoFsyncS2MBus0bj | ReadControlM2SBus0bj | WriteControlM2SBus0bj

#### **Parameters**

#### Control protocol — Protocol interface selection

Data stream (default) | Pixel stream | Random access read | Random access write

Specify the protocol interface as one of these values:

- Data stream Use this protocol if you require AXI4 data stream.

- Pixel stream Use this protocol if you require AXI4 video stream.

- Random access read Use this protocol if you require AXI4 read.

- Random access write Use this protocol if you require AXI4 write.

The input ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-2.

#### Control type — Control type selection

Valid (default) | Ready | Ready with frame sync

Specify the type of control.

To enable the Ready with frame sync option, set the **Control protocol** parameter to Pixel stream.

The input ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-2.

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

### **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer  $^{\text{\tiny TM}}$ .

#### See Also

SoC Bus Selector

Introduced in R2019a

## **SoC Bus Selector**

Convert bus to control signals

**Library:** SoC Blockset / Hardware Logic Connectivity

## **Description**

The SoC Bus Selector block converts a set of control signals from a bus. The block accepts a bus and outputs control signals.

You can configure this block to support multiple protocol interface types. Parameter and port configurations for this block vary based on your desired protocol interface type and mode of operation, as outlined in this table.

| Protocol<br>Interface<br>Type | Mode of Operation    | Parameter<br>Configuration                                               | Enabled Output Ports          |

|-------------------------------|----------------------|--------------------------------------------------------------------------|-------------------------------|

| Data stream                   | Read stream<br>data  | Set Control protocol<br>to Data stream and<br>Control type to<br>Valid.  | valid<br>tlast                |

|                               | Write stream<br>data | Set Control protocol to Data stream and Control type to Ready.           | ready                         |

| Pixel stream                  | Read video<br>stream | Set Control protocol<br>to Pixel stream and<br>Control type to<br>Valid. | hStart hEnd vStart vEnd valid |

| Protocol<br>Interface<br>Type | Mode of<br>Operation  | Parameter<br>Configuration                                             | Enabled Output Ports           |

|-------------------------------|-----------------------|------------------------------------------------------------------------|--------------------------------|

|                               | Write video<br>stream | Set Control protocol to Pixel stream and Control type to Ready.        | ready                          |

| Random<br>access read         | Read data             | Set Control protocol to Random access read and Control type to Valid.  | rd_aready<br>rd_dvalid         |

| Random<br>access write        | Write data            | Set Control protocol to Random access write and Control type to Ready. | wr_ready wr_bvalid wr_complete |

## **Ports**

## Input

#### ctrlBus — Input control bus

bus

Input control bus, specified as a bus.

The data type of the input control bus depends on the values of the **Control protocol** and **Control type** parameters.

| Parameter Configuration                                                       | Input Data Type |

|-------------------------------------------------------------------------------|-----------------|

| Set <b>Control protocol</b> to Data stream and <b>Control type</b> to Valid.  | StreamM2SBusObj |

| Set <b>Control protocol</b> to Data stream and <b>Control type</b> to Ready.  | StreamS2MBus0bj |

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Valid. | pixelcontrol    |

| Parameter Configuration                                                              | Input Data Type       |

|--------------------------------------------------------------------------------------|-----------------------|

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Ready.        | StreamVideoS2MBusObj  |

| Set <b>Control protocol</b> to Random access read and <b>Control type</b> to Valid.  | ReadControlS2MBus0bj  |

| Set <b>Control protocol</b> to Random access write and <b>Control type</b> to Ready. | WriteControlS2MBus0bj |

Data Types: StreamM2SBusObj | StreamS2MBusObj | pixelcontrol | StreamVideoS2MBusObj | ReadControlS2MBusObj | WriteControlS2MBusObj

#### **Output**

#### valid — Valid control signal

Boolean scalar

Valid control signal, returned as a scalar. You can use this port for data stream and pixel stream protocols only.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either **Data** stream or **Pixel** stream and the **Control type** parameter to **Valid**.

Data Types: Boolean

#### tlast — Indication of end of data packet

Boolean scalar

Indication of end of the data packet, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Data stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### ready - Ready control signal

Boolean scalar

Ready control signal, returned as a Boolean scalar. This port is available for Data stream and Pixel stream control protocols.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Ready.

Data Types: Boolean

#### hStart — First pixel in horizontal line of frame

Boolean scalar

First pixel in a horizontal line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### hEnd — Last pixel in horizontal line of frame

Boolean scalar

Last pixel in a horizontal line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### vStart — First pixel in first (top) line of frame

Boolean scalar

First pixel in the first (top) line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### vEnd — Last pixel in last (bottom) line of frame

Boolean scalar

Last pixel in the last (bottom) line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### rd\_aready — Accept read requests

Boolean scalar

Accept read requests, returned as a scalar. It indicates when to accept read requests.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### rd\_dvalid — Read request valid

Boolean scalar

Read request valid, returned as a Boolean scalar. It is the control signal that indicates the data returned from the read request is valid.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### wr\_ready — Write ready signal

Boolean scalar

Write ready signal, returned as a Boolean scalar. It corresponds to the backpressure from the slave IP core or external memory. When this value is  $1 \, (high)$ , it indicates that data can be sent. When this value is  $0 \, (low)$ , it indicates that the hardware logic must stop sending data within one clock cycle.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### wr\_bvalid — Write valid signal

Boolean scalar

Write valid signal, returned as a Boolean scalar. It is the response signal from the slave IP core that you can use for diagnosis purposes. This value becomes 1 (high) after the AXI4 interconnect accepts each burst transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### wr complete — Write transaction complete

Boolean scalar

Write transaction complete, specified as a Boolean scalar. It is the control signal that when remains high for one clock cycle indicates that the write transaction has completed. This signal asserts at the last wr bvalid of the burst.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### **Parameters**

#### Control protocol — Protocol interface selection

Data stream (default) | Pixel stream | Random access read | Random access write

Specify the protocol interface as one of these values:

- Data stream Use this protocol if you require AXI4 data stream.

- Pixel stream Use this protocol if you require AXI4 video stream.

- Random access read Use this protocol if you require AXI4 read.

- Random access write Use this protocol if you require AXI4 write.

The output ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-10.

#### Control type — Control type selection

Valid (default) | Ready

Specify the type of control.

The output ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-10.

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder $^{\text{\tiny TM}}$ .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer™.

#### See Also

SoC Bus Creator

Introduced in R2019a

## Stream FIFO

Control backpressure between hardware logic and upstream data interface

**Library:** SoC Blockset / Hardware Logic Connectivity

dataln adataOut

dValidIn FIFO dValidOut

rdyToUp rdyFromDown

Stream FIFO

## **Description**

The Stream FIFO block controls the backpressure from the hardware logic to the upstream data interface. It also controls the flow between the upstream and downstream data interfaces of the hardware logic. Integrate this block as a configurable first-in, first-out (FIFO) block for AXI4 data stream applications. The block enables you to configure its depth and set its almost full threshold value.

#### **Ports**

#### Input

#### dataIn — Input stream data

scalar

Input stream data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

#### ${\tt dValidIn-Indication\ of\ valid\ input\ stream\ data}$

Boolean scalar

Control signal that indicates if the input stream data from the data source is valid. When this value is 1 (true), the block accepts the values on the **dataIn** port. When this value is  $\theta$  (false), the block ignores the values on the **dataIn** port.

Data Types: Boolean

#### rdyFromDown — Ready signal from downstream interface

Boolean scalar

Control signal that indicates if the block can send stream data to the downstream interface. When this value is 1 (true), the downstream interface is ready, and the block can send the stream data. When this value is  $\theta$  (false), the downstream interface is not ready, and the block cannot send the stream data.

Data Types: Boolean

#### Output

#### dataOut — Output stream data

scalar

Output stream data to the downstream interface. The data type of this output data is the same as the data type of the input data.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

#### dValidOut — Indication of valid output stream data

Boolean scalar

Control signal that indicates if the output stream data is valid. When this value is 1 (true), the output stream data on the **dataOut** port is valid. When this value is  $\theta$  (false), the output stream data on the **dataOut** port is not valid.

Data Types: Boolean

#### rdyToUp — Ready signal to upstream interface

Boolean scalar

Control signal that indicates if the block is ready to receive stream data from the upstream interface. When this value is 1 (true), the block is ready to accept stream data from the upstream interface. When this value is 0 (false), the block is not ready to accept stream data from the upstream interface.

Data Types: Boolean

#### **Parameters**

#### Depth of FIFO - FIFO depth

16 (default) | positive integer

Specify the depth of the FIFO. This value must be a positive integer and is the maximum number of entries that can be buffered before data gets dropped.

#### Almost full threshold — Almost full threshold value

8 (default) | positive integer

Specify a value that asserts a back-pressure signal from the block to the data source.

To avoid dropping data, set a value allowing the data source enough time to react to backpressure. This value must be a positive integer and smaller than the FIFO depth.

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder  $^{\text{\tiny TM}}$ .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

### **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer  $^{\scriptscriptstyle{\text{TM}}}.$

#### See Also

Video Stream FIFO

Introduced in R2019a

## Video Stream FIFO

Control backpressure between hardware logic and upstream video interface

**Library:** SoC Blockset / Hardware Logic Connectivity

pixelIn pixelOut

ctrlIn FIFO CtrlOut

rdyToUp rdyFromDown

Video Stream FIFO

## **Description**

The Video Stream FIFO block controls the back-pressure from the hardware logic to the upstream video interface. It also controls the flow between the upstream and downstream pixel data interfaces of hardware logic. Integrate this block as a configurable first-in, first-out (FIFO) block for AXI4 video stream applications. The block enables you to configure its depth and set its almost full threshold value.

#### **Ports**

#### Input

#### pixelIn — Input pixel data

scalar

Input pixel data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

#### ctrlIn — Control signals accompanying input pixel data

pixelcontrol bus

Control signals accompanying the pixel stream, specified as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame.

Data Types: pixelcontrol

#### rdyFromDown — Ready signal from downstream interface

Boolean scalar

Control signal that indicates if the block can send pixel data to the downstream interface. When this value is 1 (true), the downstream interface is ready, and the block can send the pixel data. When this value is 0 (false), the downstream interface is not ready, and the block cannot send the pixel data.

Data Types: Boolean

#### **Output**

#### pixelOut — Output pixel data

scalar

Output pixel data to the downstream interface. The data type of this output data is the same as the data type of the input data.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

#### ctrlOut — Control signals accompanying output pixel data

pixelcontrol bus

Control signals accompanying output pixel stream, returned as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame.

Data Types: pixelcontrol

#### rdyToUp — Ready signal to upstream interface

Boolean scalar

Control signal that indicates if the block is ready to receive pixel data from the upstream interface. When this value is 1 (true), the block is ready to accept pixel data from the upstream interface. When this value is 0 (false), the block is not ready to accept pixel data from the upstream interface.

Data Types: Boolean

#### **Parameters**

#### Depth of FIFO - FIFO depth

16 (default) | positive integer

Specify the depth of the FIFO. This value must be a positive scalar integer and is the maximum number of entries that can be buffered before data gets dropped.

#### Almost full threshold — Almost full threshold value

8 (default) | positive integer

Specify a value that asserts a back-pressure signal from the block to the data source.

To avoid dropping data, set a value allowing the data source enough time to react to backpressure. This value must be a positive integer and smaller than the FIFO depth.

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder  $^{\text{\tiny TM}}$ .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer  $^{\text{\tiny TM}}$  .

#### See Also

Stream FIFO

Introduced in R2019a

## **Video Stream Connector**

Connect two IPs with video streaming interfaces **Library:** SoC Blockset / Hardware Logic Connectivity

## **Description**

The Stream Connector block connects two IPs with video streaming interfaces. Use this block in the FPGA model of an SoC application to connect two IPs.

#### **Ports**

#### Input

#### wrData — Input video data

scalar

Input video data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

## wrCtrlIn — Input control signals accompanying pixel stream

pixelControl bus

Control signals accompanying the pixel stream, specified as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame. For additional information about the pixelcontrol bus type, see "AXI4-Stream Video Interface".

Data Types: pixelcontrol

#### rdCtrlIn — Ready signal from downstream interface

boolean scalar

Control signal that indicates if the block can send video data to downstream interface. When this value is (true), the downstream block is ready to receive data.

#### **Output**

#### rdData — Output video data

scalar

Output video data to the downstream destination IP.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

## rdCtrlOut — Output control signals accompanying output pixel stream pixelcontrol bus

Control signals accompanying the output video data, specified as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame.

Data Types: pixelcontrol

#### wrCtrlOut — Ready signal to the upstream interface

boolean scalar

Control signal that indicates that the block can receive stream data from upstream interface.

Data Types: Boolean

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder $^{\text{\tiny IM}}$ .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer™.

## **See Also**

Stream Connector

Introduced in R2019a

## **Stream Connector**

Connect two IPs with data streaming interfaces **Library:** SoC Blockset / Hardware Logic Connectivity

## **Description**

The Stream Connector block connects two IPs with data streaming interfaces. Use this block in the FPGA model of an SoC application to connect two IPs.

#### **Ports**

### Input

#### wrData - Input stream data

scalar

Input stream data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

#### wrValid — Indication of valid input stream data

boolean scalar

Control signal that indicates if the input data from the data source is valid. When this value is (true), the block accepts the values on the **wrData** port. When this value is (false), the block ignores the value on the **wrData** port.

Data Types: Boolean

#### wrLast - Indication of last beat in burst

boolean scalar

Control signal that indicates the last beat of data from the upstream IP.

Data Types: Boolean

#### rdReady — Ready signal from downstream interface

boolean scalar

Control signal that indicates if the block can send stream data to the downstream interface. When this value is (true), the downstream block is ready to receive data.

Data Types: Boolean

#### **Output**

#### rdData — Output stream data

scalar

Output stream data to the downstream destination IP.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

#### rdValid — Indication of valid output stream data

boolean scalar

Control signal that indicates if the output stream data is valid.

Data Types: Boolean

#### rdLast - Indicates last beat in burst

boolean scalar

Control signal that indicates that the output stream data now has last beat of burst data.

Data Types: Boolean

#### wrReady — Ready signal to upstream interface

boolean scalar

Control signal that indicates if the block can receive stream data from the upstream interface.

Data Types: Boolean

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer™.

## See Also

Video Stream Connector

Introduced in R2019a

## **DIP Switch**

Connect signals attached to DIP switches on hardware board **Library:** SoC Blockset / Hardware Logic I/O

## **Description**

The DIP Switch block controls the hardware logic. The hardware logic signals connected to a DIP Switch block are equivalent to the signals connected to the Dual Inline Package (DIP) switches on the hardware board.

**Note** Intel® hardware boards operate with active low signals. When you select an Intel hardware board, the DIP Switch block accepts or outputs active low inputs and it represents the port names prefixed with letter "n". For example, **nDS1**.

#### **Ports**

#### Input

#### DSInx — Input signal

Boolean scalar

Input signal to control the hardware logic. Using this port, you can dynamically control the hardware logic during simulation at run time. There is a port for each DIP switch, named **DSIn1** to **DSInx**, where x is **Number of DIP switches**.

**Note** When you select an Intel hardware board, you must provide inputs in active low mode.

#### **Dependencies**

To enable this port, set the **Specify DIP switches via** parameter to InputPort.

Data Types: Boolean

#### Output

#### DSx - Output signal

Boolean scalar

Output signal that returns the state of the switch. There is a port for each DIP switch, named **DS1**to **DS***x*, where *x* is **Number of DIP switches**.

Data Types: Boolean

## **Parameters**

#### Hardware board — View selected hardware

None (default) | supported Xilinx or Intel boards

This parameter is read-only. To choose a hardware board and configure board parameters, see "Hardware Implementation Pane" on page 2-2.

#### View DIP switches location — View DIP switches

button

To view a diagram with the location of the DIP switches on the selected hardware board, click the **View DIP switches location** button.

#### Specify DIP switches via — DIP switch source

Dialog (default) | InputPort

To control the hardware logic by using the block parameters, select Dialog. To control the hardware logic from the input port, select InputPort.

#### Number of DIP switches — DIP switch selection

1 (default) | list of integers in the range [1, n]

To specify the required number of DIP switch ports, select a value from the **Number of DIP switches** list. n represents the number of available DIP switches on the specified hardware board.

For example, if you select 3 from the list, the block shows three DIP switch ports.

#### DIP switches

#### DSn — Selected DIP switches

Off (default) | On

To enable the nth DIP switch port, select **On** for the DSn parameter. n represents the number of available DIP switches on the specified hardware board.

#### **Dependencies**

To enable this parameter, set the **Specify DIP switches via** parameter to Dialog.

#### Sample time — System sample time

-1 (default) | positive scalar

Specify the time interval a DIP switch toggles between On and Off.

# **Extended Capabilities**

## **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder $^{\text{\tiny IM}}$ .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer  $^{\text{\tiny TM}}$ .

## See Also

LED | Push Button

# **12C Master**

Configure and communicate with I2C slave device **Library:** SoC Blockset / Hardware Logic I/O

# **Description**

The I2C Master block configures and communicates with an inter-integrated circuit communications (I2C) slave device connected to a field programmable gate array (FPGA). This block contains an I2C master controller with an AXI-Lite interface to perform the configuration.

The I2C Master block supports these features:

- AXI4-Lite interface support for configuration and access

- Single-master and multi-slave support

- 7-bit addressing support

- Multiple transmission speeds support, which includes these modes:

- Standard mode (up to100 kHz)

- Fast mode (up to 400 kHz)

- Fast-plus mode (up to 1 MHz)

- Burst mode support with a maximum burst size of 16 bytes

- An HDL-IP compatible model with code generation capability

The block uses the AXI-Lite interface to configure and create a control path interface to communicate with an I2C slave device. The block enables you to perform simulation and generation processes separately. The hardware generated from the generation process

contains an AXI-Lite register interface and two hardware interfaces, serial clock (SCL) and serial data (SDA). SCL and SDA connect the I2C Master block and the slave device.

Each port represented in the block is an AXI-Lite register, except the **sdaIn**, **scl**, and **sda** ports. To communicate with the slave device, the AXI-Lite register interface configures the register information in the I2C Master block. This table contains the I2C Master AXI-Lite register information.

| Address | Port and Register<br>Name                  | Register<br>Size in Bits | Operation Mode |

|---------|--------------------------------------------|--------------------------|----------------|

| 0x100   | ctrlInf — Control information              | 32                       | Write          |

| 0x104   | slvAddr — Slave<br>address                 | 32                       | Write          |

| 0x108   | regAddr — Register address                 | 32                       | Write          |

| 0x10C   | dataReg — First data<br>register           | 32                       | Write          |

| 0x110   | dataReg1 — Second data register            | 32                       | Write          |

| 0x114   | dataReg2 — Third data register             | 32                       | Write          |

| 0x118   | dataReg3 — Fourth data register            | 32                       | Write          |

| 0x11C   | <b>userRdy</b> — User-ready register       | 32                       | Write          |

| 0x120   | <b>done</b> — Done register                | 32                       | Write          |

| 0x124   | rdy — Ready register                       | 32                       | Read           |

| 0x128   | respData — First<br>response data register | 32                       | Read           |

| 0x12C   | respData1 — Second response data register  | 32                       | Read           |

| 0x130   | respData2 — Third response data register   | 32                       | Read           |

| Address | Port and Register<br>Name                          | Register<br>Size in Bits | Operation Mode |

|---------|----------------------------------------------------|--------------------------|----------------|

| 0x134   | respData3 — Fourth response data register          | 32                       | Read           |

| 0x138   | <b>validData</b> — Response<br>data valid register | 32                       | Read           |

# **Ports**

## Input

#### ctrlInf — Control information

scalar

Control information register that contains configuration information on how the block communicates with the slave device. Specify this value as a scalar, as described in this table. You can modify the configuration based on your requirement.

| Bit   | Purpose                                                | Value Description                                                                                                                                                                                                                                                              |

|-------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Set write or read mode.                                | To write to the slave-device register, set this value to 0. To read from the slave-device register, set this value to 1.                                                                                                                                                       |

| [2:1] | Set the size of the slave-<br>device register address. | <ul> <li>If the slave-device register address size is:</li> <li>One byte (8 bits), set this value to 00</li> <li>Two bytes (16 bits), set this value to 01</li> <li>Three bytes (24 bits), set this value to 10</li> <li>Four bytes (32 bits), set this value to 11</li> </ul> |

| Bit | Purpose                                         | Value Description                                |

|-----|-------------------------------------------------|--------------------------------------------------|

|     | Set the data size of the slave-device register. | If the slave-device register supports:           |

|     |                                                 | One byte of data, set this value to 0000         |

|     |                                                 | Two bytes of data, set this value to 0001        |

|     |                                                 | Three bytes of data, set this value to 0010      |

|     |                                                 | • Four bytes of data, set this value to 0011     |

|     |                                                 | • Five bytes of data, set this value to 0100     |

|     |                                                 | Six bytes of data, set this value to 0101        |

|     |                                                 | • Seven bytes of data, set this value to 0110    |

|     |                                                 | • Eight bytes of data, set this value to 0111    |

|     |                                                 | Nine bytes of data, set this value to 1000       |

|     |                                                 | • Ten bytes of data, set this value to 1001      |

|     |                                                 | • Eleven bytes of data, set this value to 1010   |

|     |                                                 | Twelve bytes of data, set this value to 1011     |

|     |                                                 | • Thirteen bytes of data, set this value to 1100 |

|     |                                                 | • Fourteen bytes of data, set this value to 1101 |

|     |                                                 | • Fifteen bytes of data, set this value to 1110  |

|     |                                                 | • Sixteen bytes of data, set this value to 1111  |

| 7   | Reserved                                        | Reserved                                         |

Data Types: uint8

#### slvAddr — Slave address

scalar

Slave-address register that contains the address of the slave device, specified as a scalar.

Data Types: uint32

#### regAddr — Register address

scalar

Specify the register address of the slave device as a scalar.

Data Types: uint32

#### dataReg - First data register

scalar

First data register that the block uses to write the first 4 bytes of data to the slave-device register, specified as a scalar. This register includes the least significant bit (LSB).

Data Types: uint32

#### dataReg1 — Second data register

scalar

Second data register that the block uses to write the second set of 4 bytes of data to the slave-device register, specified as a scalar.

Data Types: uint32

## dataReg2 — Third data register

scalar

Third data register that the block uses to write the third set of 4 bytes of data to the slave-device register, specified as a scalar.

Data Types: uint32

## dataReg3 — Fourth data register

scalar

Fourth data register that the block uses to write the fourth set of 4 bytes of data to the slave-device register, specified as a scalar. This register includes the most significant bit (MSB).

Data Types: uint32

#### userRdy — User-ready signal

Boolean scalar

User-ready signal, specified as a Boolean scalar. When this value is  $\mathbf{1}$  (true), the user is ready to read the response data from the block. When this value is  $\mathbf{0}$  (false), the user is not ready to read the response data from the block.

Data Types: Boolean

#### done — Done signal

Boolean scalar

Done signal, specified as a Boolean scalar. This value indicates the block when to read the AXI-Lite register information.

Set this value to 1 (true) after sending one set of register information to the block. The block reads the AXI-Lite register information only when you set this value to 1. Set this value to 0 (false) immediately after this operation.

One set of register information is a combination of **ctrlInf** (Control information), **slvAddr** (Slave address), **regAddr** (Register address), and **dataReg**, **dataReg1**, **dataReg2**, and **dataReg3** (Data registers).

Data Types: Boolean

#### sdaIn — Input serial data

Boolean scalar

Input serial data, specified as a Boolean scalar. This port provides a serial data signal to the block from the slave device.

#### **Dependencies**

To enable this port, set the **Type of model** parameter to Simulation.

Data Types: Boolean

## **Output**

#### scl — Output serial clock

Boolean scalar

Output serial clock, returned as a Boolean scalar. This port provides a serial clock signal from the block to the slave device.

Data Types: Boolean

#### sda — Output serial data

Boolean scalar

Output serial data, returned as a Boolean scalar. This port provides a serial data signal from the block to the slave device.

Data Types: Boolean

#### rdy - Ready signal

Boolean scalar

Ready signal, returned as a Boolean scalar. When this value is  $\mathbf{1}$  (true), the block is ready to accept the configuration data. When this value is  $\mathbf{0}$  (false), the block is not ready to accept the configuration data.

Data Types: Boolean

#### respData — First response data register

scalar

First response data register that contains the first 4 bytes of data from the slave-device register, returned as a scalar. This register includes the least significant bit (LSB).

Data Types: uint32

#### respData1 — Second response data register

scalar

Second response data register that contains the second set of 4 bytes of data from the slave-device register, returned as a scalar.

Data Types: uint32

## respData2 — Third response data register

scalar

Third response data register that contains the third set of 4 bytes of data from the slave-device register, returned as a scalar.

Data Types: uint32

#### respData3 — Fourth response data register

scalar

Fourth response data register that contains the fourth set of 4 bytes of data from the slave-device register, returned as a scalar. This data includes the most significant bit (MSB).

Data Types: uint32

#### validData — Indication of valid response data

Boolean scalar

Control signal that indicates if the response data is valid, returned as a Boolean scalar. When this value is 1 (true), the response data from response data registers is valid. When this value is  $\theta$  (false), the response data from response data registers is not valid.

Data Types: Boolean

## **Parameters**

## Type of model — Model-type selection

Generation (default) | Simulation

Specify the model type.

- To use this block for simulation purposes, set this parameter to Simulation.

- To use this block for generation purposes, set this parameter to Generation. The generation process creates a hardware IP with AXI-Lite interface, SCL, and SDA interfaces.

## Speed — Speed-mode selection

Standard Mode (default) | Fast Mode | Fast Plus Mode

Specify the speed mode as one of these values:

- Standard Mode — Supports frequencies up to 100 KHz

- Fast Mode Supports frequencies up to 400 KHz

- Fast Plus Mode Supports frequencies up to 1 MHz

# **Extended Capabilities**

# **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer™.

# **See Also**

## **LED**

Connect signals attached to LEDs on hardware board **Library:** SoC Blockset / Hardware Logic I/O

# **Description**

The LED block indicates the status of a signal. The hardware logic signals connected to an LED block are equivalent to the signals connected to the Light Emitting Diodes (LED) on the hardware board.

**Note** Intel hardware boards operate with active low signals. When you select an Intel hardware board, the LED block accepts active low inputs and it represents the port names prefixed with letter "n". For example, **nLED1**.

## **Ports**

## Input

LEDx — Input signal

Boolean scalar

Input signal from the hardware logic. There is a port for each LED, named **LED1** to **LEDx**, where x is **Number of LEDs**.

Data Types: Boolean

## **Parameters**

#### Hardware board — View selected hardware

None (default) | supported Xilinx or Intel boards

This parameter is read-only. To choose a hardware board and configure board parameters, see "Hardware Implementation Pane" on page 2-2.

#### View LEDs location — View LEDs

button

To view a diagram of the location of the LEDs on the selected hardware board, click the **View LEDs location** button.

#### Number of LEDs — LED selection

1 (default) | list of integers in the range [1, n]

To specify the required number of LED ports, select a value from the **Number of LEDs** list. n represents the number of available LEDs on the specified hardware board.

For example, if you select 4 from the list, the block shows four LED ports.

# **Extended Capabilities**

## **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

# **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer  $^{\text{\tiny TM}}$ .

## See Also

DIP Switch | Push Button

# **Push Button**

Connect signals attached to push buttons on hardware board **Library:** SoC Blockset / Hardware Logic I/O

# **Description**

The Push Button block controls the hardware mechanism. The hardware logic signals connected to a Push Button block are equivalent to the signals connected to the push buttons on the hardware board.

**Note** Intel hardware boards operate with active low signals. When you select an Intel hardware board, the Push Button block accepts or outputs active low inputs and it represents the port names prefixed with letter "n". For example, **nPB1**.

## **Ports**

## Input

## PBInx — Input signal

Boolean scalar

Input signal to control the hardware logic. Using these ports, you can dynamically control the hardware logic during simulation at run time. There is a port for each push button, named **PBIn1**to **PBInx**, where x is **Number of push buttons**.

**Note** When you select an Intel hardware board, you must provide inputs in active low mode.

#### **Dependencies**

To enable this port, set the **Specify push buttons via** parameter to **InputPort**.

Data Types: Boolean

## Output

#### PBx - Output signal

Boolean scalar

Output signal that returns the state of the push button. There is a port for each push button, named **PB1**to **PB**x, where x is **Number of push buttons**.

Data Types: Boolean

## **Parameters**

#### Hardware board — View selected hardware

None (default) | supported Xilinx or Intel boards

This parameter is read-only. To choose a hardware board and configure board parameters, see "Hardware Implementation Pane" on page 2-2.

## View push buttons location — View push buttons

button

To view a diagram of the location of the push buttons on the selected hardware board, click the **View push buttons location** button.

## Specify push buttons via — Push-button source

Dialog (default) | InputPort

To control the hardware logic by using the block parameters, select <code>Dialog</code>. To control the hardware logic from the input port, select <code>InputPort</code>.

## Number of push buttons — Push-button selection

1 (default) | list of integers in the range [1, n]

To specify the required number of push-button ports, select a value from the **Number of push buttons** list. n represents the number of available push buttons on the specified hardware board.

For example, if you select 3 from the list, the block shows three push-button ports.

#### **Push buttons**

#### **PB***n* — Selected push buttons

Off (default) | On

To enable the *n*th push-button port, select **On** for the PB*n* parameter. *n* represents the number of available push buttons on the specified hardware board.

#### **Dependencies**

To enable this parameter, set the **Specify push buttons via** parameter to Dialog.

#### Sample time — Sampling interval

-1 (default) | positive scalar

Specify the time interval a push button toggles between On and Off.

# **Extended Capabilities**

## **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder  $^{\scriptscriptstyle\mathsf{TM}}$  .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer  $^{\scriptscriptstyle{\text{TM}}}$ .

## See Also

DIP Switch | LED

# **AXI4 Master Sink**

Receive random access memory data

**Library:** SoC Blockset / Hardware Logic Testbench

# **Description**

The AXI4 Master Sink block receives random access memory data from advanced extensible interface AXI4-based data interface blocks. You can use this block as a test sink block for simulating AXI4-based data applications.

The block accepts data along with a control bus and outputs a control bus.

## **Ports**

## Input

## rdData — Input data

scalar | vector

Input data from the data source. This value must be a scalar or vector.

Before reading the data, set the required data type. To set the data type, see the **Data type** parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

## rdCtrlIn — Input control bus

bus

Input control bus from the data producer, specified as a bus. This control bus comprises these control signals:

- rd aready Indicates the data source accepted the read request

- rd\_dvalid Indicates the data returned for the read request is valid

Data Types: ReadControlS2MBus0bj

## **Output**

#### rdCtrlOut — Output control bus

bus

Output control bus to the data source indicating the block is ready to accept data, returned as a scalar. This control bus comprises these control signals:

- rd\_addr Starting address for the read transaction that is sampled at the first cycle

of the transaction

- rd\_len Number of data values you want to read, sampled at the first cycle of the transaction

- rd\_avalid Control signal that specifies whether the read request is valid

- rd\_dready Control signal that indicates when the block can read data

Data Types: ReadControlM2SBusObj

## **Parameters**

## Data type — Input data type

uint8 (default) | double | single | int8 | int16 | int32 | uint16 | uint32 |

fixdt(1,16,0)

Select the data type format for the input AXI data.

Click the button to display the **Data Type Assistant**, which helps you to set the data type for the **rdData** input port. For details, see "Specify Data Types Using Data Type Assistant" (Simulink).

## Dimensions — Input data dimensions

10 (default) | positive integer | array

Specify the dimensions of the input data as a positive scalar or an array. This value defines the length of the transaction.

Example: 1 specifies a scalar sample.

Example: [10 1] specifies a vector of ten scalars.

#### Initial address — Start address

0 (default) | nonnegative scalar integer

Specify the address from which the block reads the data. This value must be a nonnegative integer.

#### Initial delay — Initial delay

0 (default) | nonnegative scalar

Specify the initial time after which the read operation starts.

#### Sample time — Time interval of sampling

1 (default) | scalar

Specify a discrete time at which the block accepts data. This value must be a scalar.

## Save data in workspace — Save to workspace

off (default) | on

Select this parameter to save the input data to the MATLAB® workspace.

## **Variable name — Workspace variable name**

simOut (default) | any MATLAB-supported variable name

Specify the workspace variable to which input data is saved. This parameter can be any MATLAB-supported variable name.

#### **Dependencies**

To enable this parameter, select the **Save data in workspace** parameter.

## See Also

**AXI4 Master Source**

# **AXI4 Master Source**

Generate random access memory data **Library:** SoC Blockset / Hardware Logic Testbench

# **Description**

The AXI4 Master Source block generates random access memory data to advanced extensible interface AXI4-based data interface blocks. You can use this block as a test source block for simulating AXI4-based data applications.

The block accepts a control bus and outputs data along with a control bus.

## **Ports**

## Input

## wrCtrlIn — Input control bus

bus

Control bus from the data consumer signaling that data consumer is ready to accept data, specified as a scalar. This control bus comprises these control signals:

- ullet wr\_ready Indicates the block can send data to the data consumer

- wr complete Indicates the write transaction has completed at the data consumer

- ullet wr\_bvalid Indicates the data consumer has accepted the transaction

Data Types: WriteControlS2MBus0bj

## **Output**

#### wrData - Output AXI data

scalar | vector

Output AXI data to the data consumer. This value is returned as a scalar or vector.

You can change the data type of the output data. For more information, see the **Data type** parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

#### wrCtrlOut — Output control bus

bus

Control bus to the data consumer, returned as a bus. This control bus comprises these control signals:

- wr addr Specifies the starting address that the block writes

- $\bullet$  wr len Specifies the number of data elements in the write transaction

- wr\_valid Indicates the data sampled at the wrData output port is valid

Data Types: WriteControlM2SBusObj

## **Parameters**

## Data type — Output data type

uint8 (default) | double | single | int8 | int16 | int32 | uint16 | uint32 |

fixdt(1,16,0)

Select the data type format for the output AXI data.

Click the button to display the **Data Type Assistant**, which helps you to set the data type for the **wrData** output port. For details, see "Specify Data Types Using Data Type Assistant" (Simulink).

## Dimensions — Output data dimensions

10 | positive scalar | array

Specify the dimensions of the output data as a positive scalar or an array. This value defines the length of the transaction.

Example: 1 specifies a scalar sample.

Example: [10 1] specifies a vector of ten scalars.

#### Initial address — Start address

0 (default) | nonnegative integer

Specify the address to which the block writes the data. This value must be a nonnegative integer.

#### Initial delay — Initial delay

0 (default) | nonnegative scalar

Specify the initial time after which the write operation starts. This value must be a nonnegative scalar.

#### Data generation — Output generation type

counter (default) | random | ones | workspace

Specify the generation type for the output as one of these values:

- counter Generate data from a counter, based on the selected data type.

- random Generate random data.

- ones Generate data with all the bits as ones, based on the selected data type.

- $\bullet \quad \text{workspace} \text{Generate data from the MATLAB workspace}. \\$

#### Counter init value — Initial counter value

0 (default) | scalar

Specify the value from which the counter starts. The valid range of counter values depends on the selected value for the **Data type** parameter. If this value is out of the valid range, it is rounded off to the nearest valid value.

For example, if **Data type** is uint8 and this value is 6.787, this value is rounded to 7.

#### **Dependencies**

To enable this parameter, set the **Data generation** parameter to counter.

#### Variable name — Workspace variable name

simOut (default) | any MATLAB-supported variable name

Specify the workspace variable from which output data is generated. This parameter can be any MATLAB-supported variable name.

**Note** The workspace variable must be a numerical array.

#### **Dependencies**

To enable this parameter, set the **Data generation** parameter to workspace.

#### Sample time — Time interval of sampling

1 (default) | scalar

Specify the discrete time at which the block outputs data. This value must be a scalar.

## See Also

**AXI4 Master Sink**

# **Stream Data Sink**

Receive continuous stream data

**Library:** SoC Blockset / Hardware Logic Testbench

# **Description**

The Stream Data Sink block receives continuous stream data from advanced extensible interface AXI4-based stream data interface blocks. You can use this block as a test sink block for simulating AXI4-based stream data applications.

The block accepts stream data along with a control bus and outputs a control bus.

# **Ports**

# Input

#### rdData — Input stream data

scalar | vector

Input stream data from the data source. This value must be a scalar or vector.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

## rdCtrlIn — Input control bus

bus

Input control bus from the data source. This control bus comprises the following control signals:

- valid Indicates the input stream data on the **rdData** input port is valid

- tlast Indicates the end of the data transaction

Data Types: StreamM2SBusObj

## **Output**

#### rdCtrlOut — Output control bus

bus

Output control bus to the data source, indicating that the block is ready to accept stream data. This control bus comprises a ready signal.

Data Types: StreamS2MBus0bj

## **Parameters**

#### Save data in workspace — Save data in workspace

off (default) | on

Select this parameter to save the input stream data to the MATLAB workspace.

#### Variable name — Workspace variable name

simOut (default) | any MATLAB-supported variable name

Specify the workspace variable to which input stream data is saved. This parameter can be any MATLAB-supported variable name.

#### **Dependencies**

To enable this parameter, select the **Save data in workspace** parameter.

# **Extended Capabilities**

## **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder $^{\text{\tiny TM}}$ .

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

# **Fixed-Point Conversion**

Convert floating-point algorithms to fixed point using Fixed-Point Designer™.

# **See Also**

Stream Data Source

# **Stream Data Source**

Generate continuous stream data

**Library:** SoC Blockset / Hardware Logic Testbench

# **Description**

The Stream Data Source block generates stream data to advanced extensible interface AXI4-based stream data interface blocks. You can use this block as a test source block for simulating AXI4-based stream data applications.

The block accepts a control bus and outputs stream data along with a control bus.

## **Ports**

# Input

## wrCtrlIn — Input control bus

bus

Control bus from the data consumer signaling that data consumer is ready to accept stream data. This control bus comprises a ready signal.

Data Types: StreamS2MBus0bj

## **Output**

#### wrData — Output stream data

scalar | vector

Output stream data to the data consumer. This value is returned as a scalar or vector.

You can change the data type of the output stream data. For more information, see the **Data type** parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

#### wrCtrlOut — Output control bus

bus

Control bus to the data consumer, returned as a bus. This control bus comprises these control signals:

- valid Indicates the output data on the **wrData** output port is valid

- tlast Indicates the end of the data transaction

Data Types: StreamM2SBusObj

## **Parameters**

#### Data type — Output data type

uint8 (default) | double | single | int8 | int16 | int32 | uint16 | uint32 |

fixdt(1,16,0)

Select the data type format for the output stream data.

Click the button to display the **Data Type Assistant**, which helps you to set the data type for the **wrData** output port. For details, see "Specify Data Types Using Data Type Assistant" (Simulink).

## Dimensions — Output data dimensions

10 (default) | positive integer | array

Specify the dimensions of the output stream data as a positive scalar or an array.

Example: 1 specifies a scalar sample.

Example:  $[10 \ 1]$  specifies a vector of ten scalars.

## **Burst length — Length of single burst**

20 (default) | positive integer

Length of the single burst, specified as a positive integer.

#### Total bursts — Total number of bursts

4 (default) | positive integer

Total number of bursts generated from the block, specified as a positive integer.

#### Data generation — Output generation type

counter (default) | random | ones | workspace

Specify the generation type for the output as one of these values:

- counter Generate data from a counter, based on the selected data type.

- random Generate a random data.

- ones Generate data with all the bits as ones, based on the selected data type.

- workspace Generate data from the MATLAB workspace.

#### Counter init value — Initial counter value

0 (default) | scalar

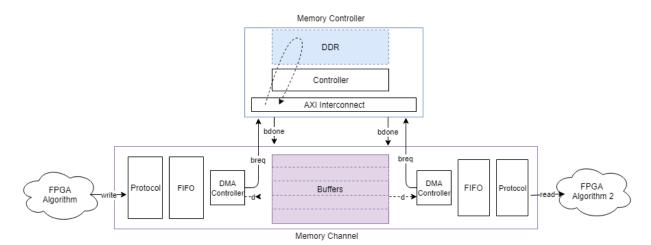

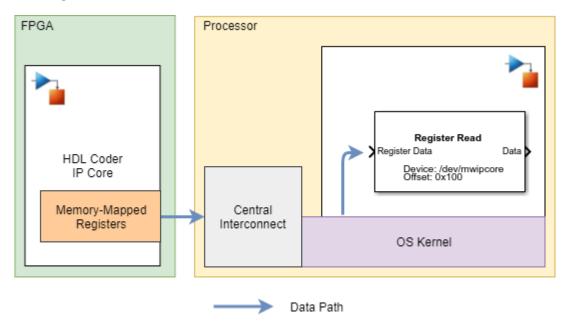

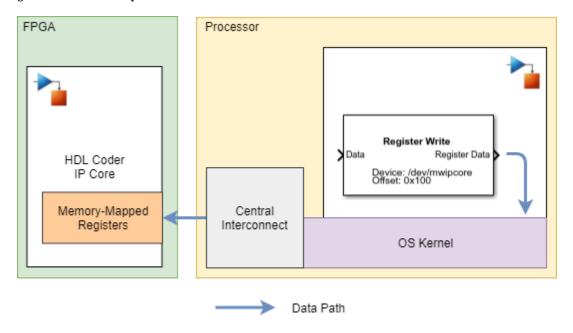

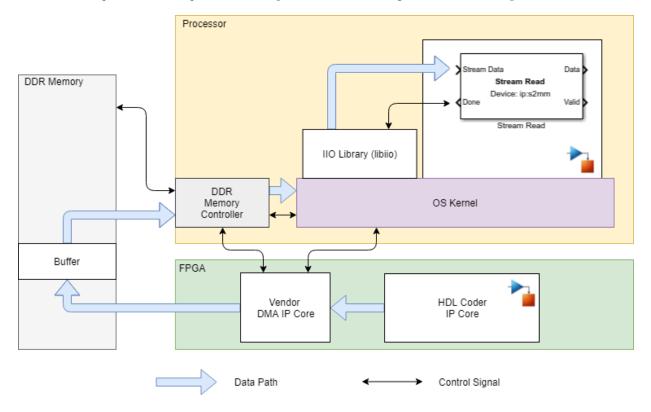

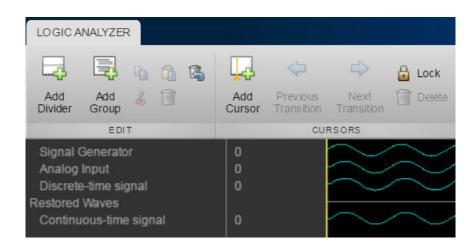

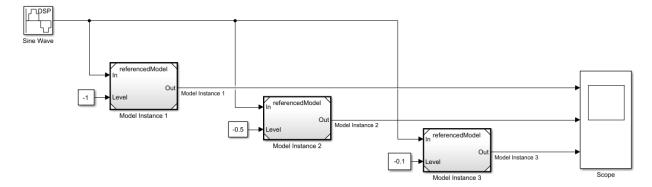

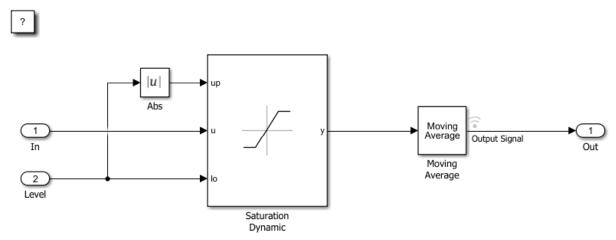

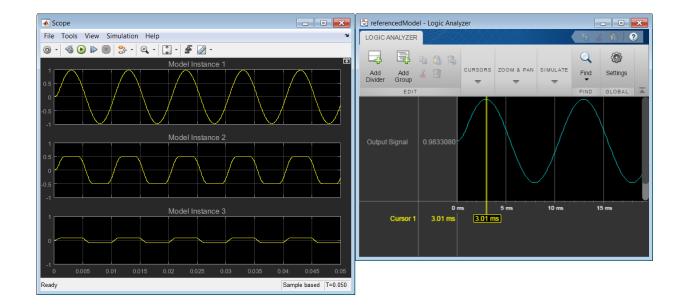

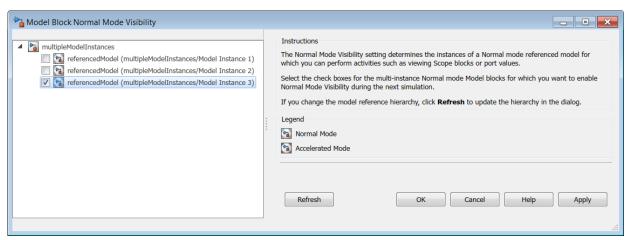

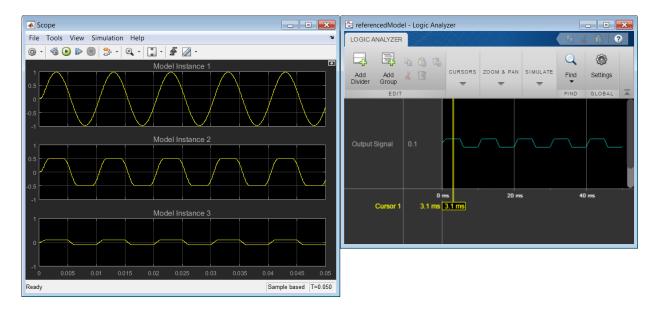

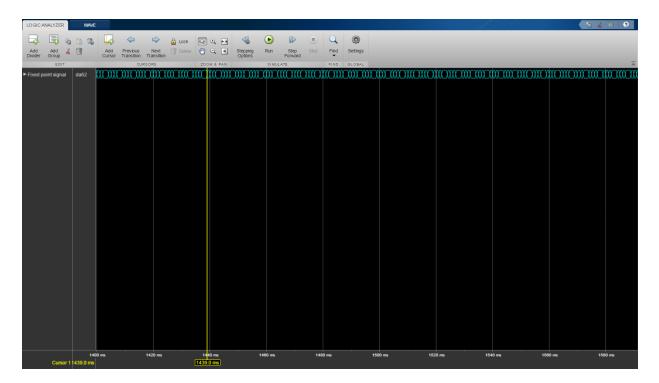

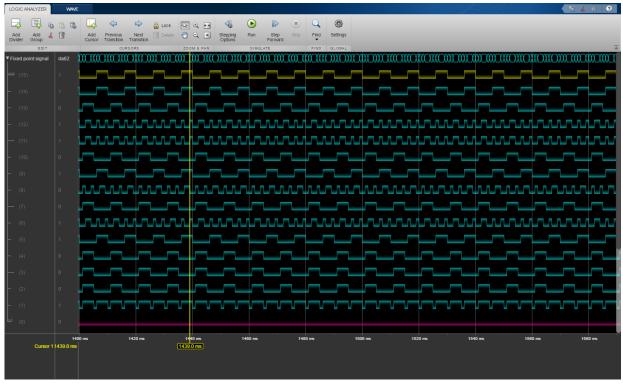

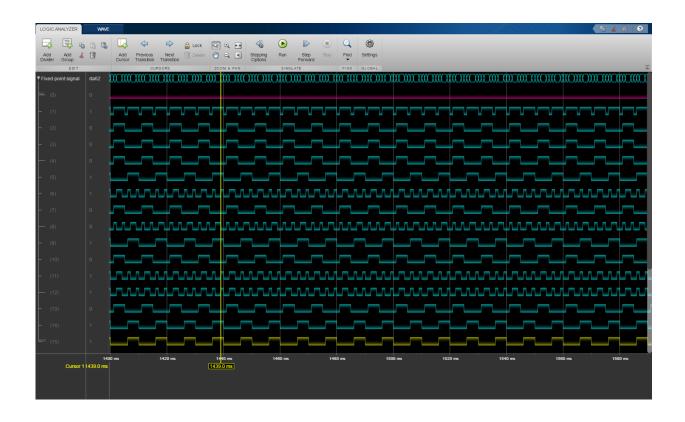

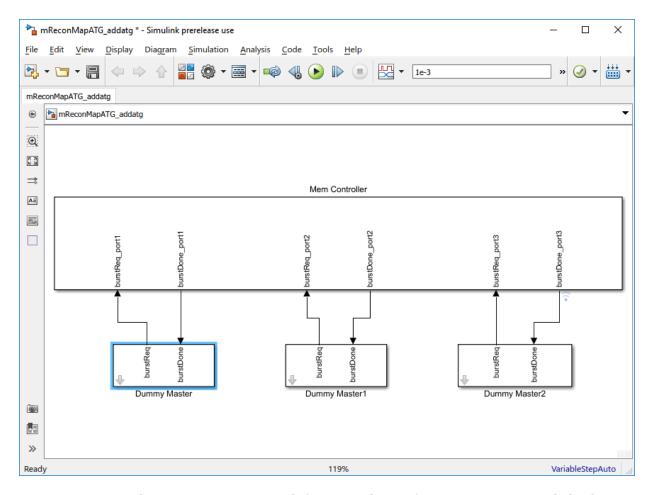

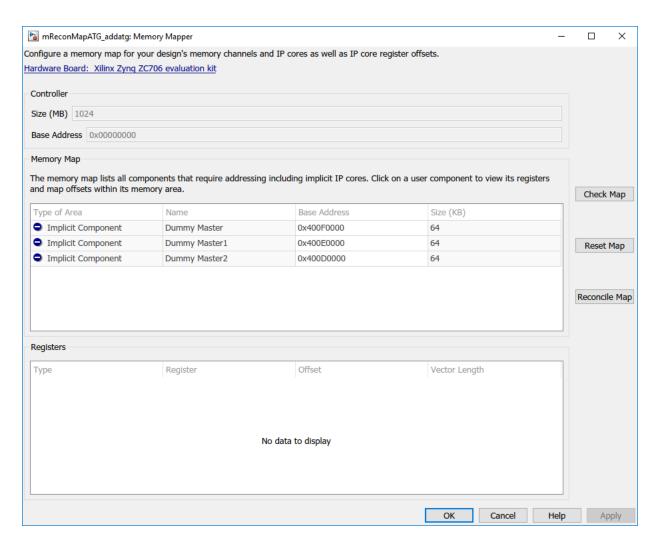

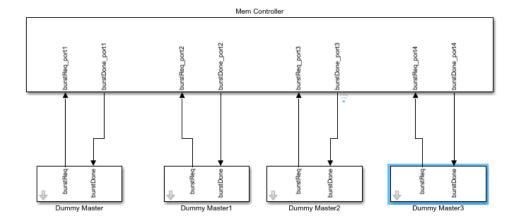

Specify the value from which the counter starts. The valid range of counter values depends on the selected value for the **Data type** parameter. If this value is out of the valid range, it is rounded off to the nearest valid value.